Lagarto: Un proyecto para el desarrollo de CPU’s y Aceleradores hardware con ISA de código abierto para la academia, la investigación y la industria.

Lagarto, es un proyecto para el diseño de CPU‘s que inicio en 2010 y que continúa en desarrollo por profesores y estudiantes del laboratorio de Microtecnología y Sistemas Embebidos del Centro de Investigación en Computación del IPN. Son varios los proyectos de investigación que han servido para ir incrementando el nivel de madurez tecnológica de la familia de procesadores lagarto. Aunque se sigue trabajando en nuevos desarrollos como: Arquitecturas Multithreading Multinúcleos, Vectoriales, y Aceleradores de IA, los dos productos de mayor madurez tecnológica son Lagarto Hun, un procesador escalar en orden y Lagarto Ka un procesador superescalar con ejecución fuera de orden.

En 2019, en alianza con el Centro Nacional de Supercomputación - BSC (Barcelona Supercomputing Center), el Departamento de Ingeniería Electrónica de la Escuela de Ingeniería en Telecomunicaciones de la Universidad Politécnica de Cataluña (UPC) y el Centro Nacional de Microelectrónica, se ha incrementado aún más la madurez tecnológica al fabricarse el primer chip de Lagarto Hun, en una tecnología de TSMC con transistores 65nm.

A partir de 2021 la Red de Investigación y Posgrado en Computación del IPN, ha decidido como una estrategia institucional poner a disposición de las academias la tecnología desarrollada, como una plataforma para la impartición de cursos de las materias de Diseño de Sistemas Digitales, Diseño VLSI, Microprocesadores, Arquitectura de Computadoras, y Sistemas Operativos.

Transmisión en Vivo

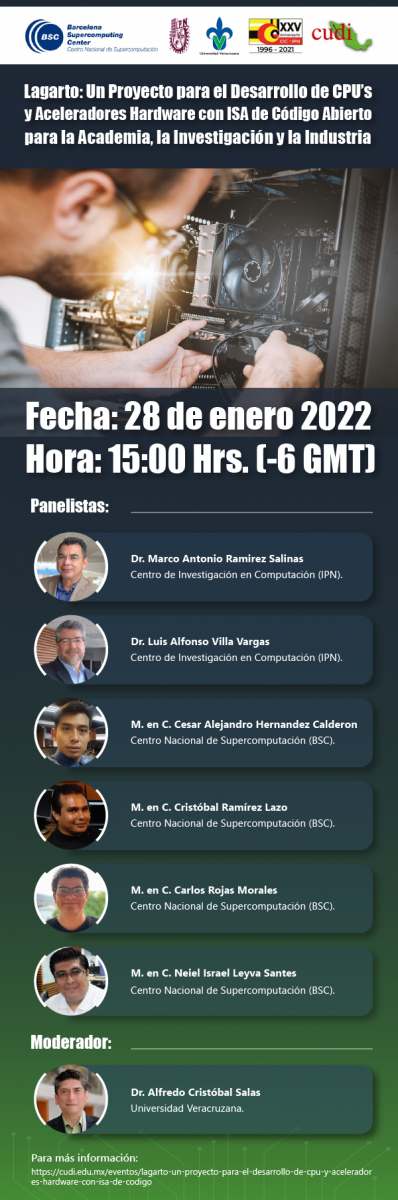

28 de enero 2022

Dinámica del evento.

El evento consiste en una serie de pláticas donde los participantes pueden aprender a utilizar las herramientas disponibles para el desarrollo de proyectos de investigación, educación, innovación o de desarrollo tecnológico basados en los procesadores Lagarto. Además, este evento busca dar a conocer los avances en el área de arquitectura de computadoras enfocada al diseño de procesadores de alto rendimiento para que la comunidad pueda detectar oportunidades de colaboración. Cada plática consiste de una exposición y una sección de pregunta-respuesta para fomentar la interacción de los participantes con los presentadores.

Resultados esperados.Un resultado importante que se espera del evento es la participación de profesores y estudiantes de nivel licenciatura o posgrado quienes quieran incursionar en el área de arquitectura de computadoras. Además, se espera que haya acuerdos de colaboración entre los asistentes para que se puedan generar proyectos educativos, técnicos, logísticos, científicos y tecnológicos que puedan detonar en una comunidad de arquitectura de computadoras que fortalezca el diseño de procesadores de alto rendimiento mexicanos.

A quién está dirigido el proyecto.

Este evento está dirigido a la comunidad universitaria y tecnológica. Además, está dirigido a los profesores-investigadores de las áreas de electrónica, robótica, así como de sistemas operativos o quienes tengan interés en hacer investigación científica y uso de los procesadores Lagarto.

Programa.

15:00 - 15:10 | Presentación del evento.- Dr. Alfredo Cristóbal Salas (UV).

15:10 – 15:30 | Procesadores Lagarto, para la academia, la investigación y la industria.- Dr. Marco Antonio Ramírez Salinas del Centro de investigación en Computación (IPN).

15:30 – 15:50 | Procesadores Lagarto como plataforma educativa.- Dr. Luis Alfonso Villa Vargas del Centro de investigación en Computación (IPN).

15:50 – 16:10 | Arquitecturas Superescalares para Sistemas Heterogéneos.- M. en C. César Alejandro Hernández Calderón del Centro Nacional de Supercomputación (BSC).

16:10 – 16:30 | Arquitecturas vectoriales y el supercómputo.- M. en C. Cristóbal Ramírez Lazo del Centro Nacional de Supercomputación (BSC).

16:30 – 16:50 | La innovación llevada al silicio.- M. en C. Carlos Rojas Morales del Centro Nacional de Supercomputación (BSC).

16:50 – 17:10 | Jerarquía de memoria para procesadores multinúcleo.- M. en C. Neiel Israel Leyva Santes del Centro Nacional de Supercomputación (BSC).

17:10 – 17:20 | Cierre del evento.- Dr. Alfredo Cristóbal Salas (UV).

Semblanzas

Dr. Marco Antonio Ramírez Salinas

Centro de investigación en Computación – IPN.

Doctor en Arquitectura de Computadoras por la Universidad Politécnica de Cataluña, España. Maestro en Ciencias en Ingeniería de Cómputo – CIC e Ingeniero en Comunicaciones y Electrónica – ESIME por el Instituto Politécnico Nacional. Profesor de tiempo completo en el Centro de Investigación en Computación en los programas de posgrado: Doctorado en Ciencias de la Computación, Maestría en Ciencias de la Computación y Maestría en Ciencias en Ingeniería de Cómputo. Desempeñó el cargo de Coordinador de la Red de Investigación en Nanociencias, Micro y Nanotecnologías. Es coordinador de la Red de Computación del IPN. Desempeñó el cargo de Director del Centro de Investigación en Computación. Es Director de Vinculación y Desarrollo Regional del IPN. SNI nivel 1.

Dr. Luis Alfonso Villa Vargas

Centro de investigación en Computación – IPN.

Doctor en Arquitectura de Computadoras por la Universidad Politécnica de Cataluña, España. Ingeniero en Comunicaciones y Electrónica y Maestro en Ciencias en Ingeniería de Cómputo por el Instituto Politécnico Nacional. Profesor de tiempo completo en el Centro de Investigación en Computación en los programas de posgrado: Doctorado en Ciencias de la Computación, Maestría en Ciencias de la Computación y Maestría en Ciencias en Ingeniería de Cómputo. Desempeño el cargo de Director del Centro de Investigación en Computación. Desempeñó el cargo de Secretario de Extensión e Integración Social del IPN. SNI nivel 1.

M en C. Cesar Alejandro Hernandez Calderon

Barcelona Supercomputing Center

Candidato a Doctor en Ciencias de la Computación por el Centro de Investigación en Computación, Obtuvo el grado de Maestro en Ciencias en Ingeniería en Microelectrónica por la Escuela Superior de Ingeniería Mecánica y Eléctrica, Culhuacán del IPN. Es Ingeniero en Mecatrónica por la Unidad Profesional Interdisciplinaria en Ingeniería y Tecnologías Avanzadas, IPN. Se desempeña como Senior Researcher en el Centro Nacional de Supercomputación (BSC), España. Es miembro del grupo de investigación Arquitectura de Computadoras y Diseño RTL. Sus líneas de investigación se enfocan en el diseño y desarrollo de procesadores superescalares de alto desempeño y bajo consumo de energía.

M en C. Cristobal Ramírez Lazo

Barcelona Supercomputing Center

Estudiante de doctorado en la Universidad Politécnica de Cataluña en el área de Arquitectura de Computadoras. Su principal línea de investigación se enfoca en arquitecturas vectoriales. Se desempeña como Research Engineer en el Centro Nacional de Supercomputación (BSC) donde es miembro del equipo de Arquitectura y Diseño RTL. Graduado de Ingeniería en Mecatrónica por la Universidad Tecnológica de la Mixteca. Obtuvo el grado de maestro en ciencias con doble reconocimiento; por el Centro de Investigación en Computación IPN y por la Universidad Politécnica de Cataluña.

M en C. Carlos Rojas Morales

Barcelona Supercomputing Center

Actualmente labora en el Centro Nacional de Supercomputación (BSC) en el departamento de Arquitectura de Computadoras para Paradigmas Paralelos, y se encuentra realizando sus estudios de doctorado en la Universidad Politécnica de Cataluña en el área de Arquitectura de Computadoras. Se graduó como Ingeniero en Comunicaciones y Electrónica del Instituto Politecnico Nacional, y como Maestro en Ciencias bajo el programa de doble Titulación por el Centro de Investigación en Computación del IPN y la Universidad Politécnica de Cataluña.

M en C. Neiel Israel Leyva Santes

Barcelona Supercomputing Center

Estudiante de doctorado en la Universidad Politécnica de Cataluña. Research Engineer en el Centro Nacional de Supercomputación (BSC). Colaborador en los proyectos: Lagarto (el primer procesador mexicano), DRAC (Designing RISC-V-based Accelerators for next generation Computers), EPI (European Processor Initiative) y MEEP (MareNostrum Experimental Exascale Platform). Miembro colaborador del laboratorio de Microtecnología y Sistemas Embebidos del Centro de Investigación en Computación del Instituto Politécnico Nacional. Sus principales líneas de investigación son jerarquía de memoria y redes de interconexión para sistemas many-core.